Design of 16-Bits and 32-Bits CPU

I have always been fascinated by how computers work. Taking the Computer Organization and Architecture course, I had the opportunity to learn the MIPS assembly language and how to design CPUs. For my final project, I designed a 16-bit CPU with Logisim and 32 CPU with VHDL.

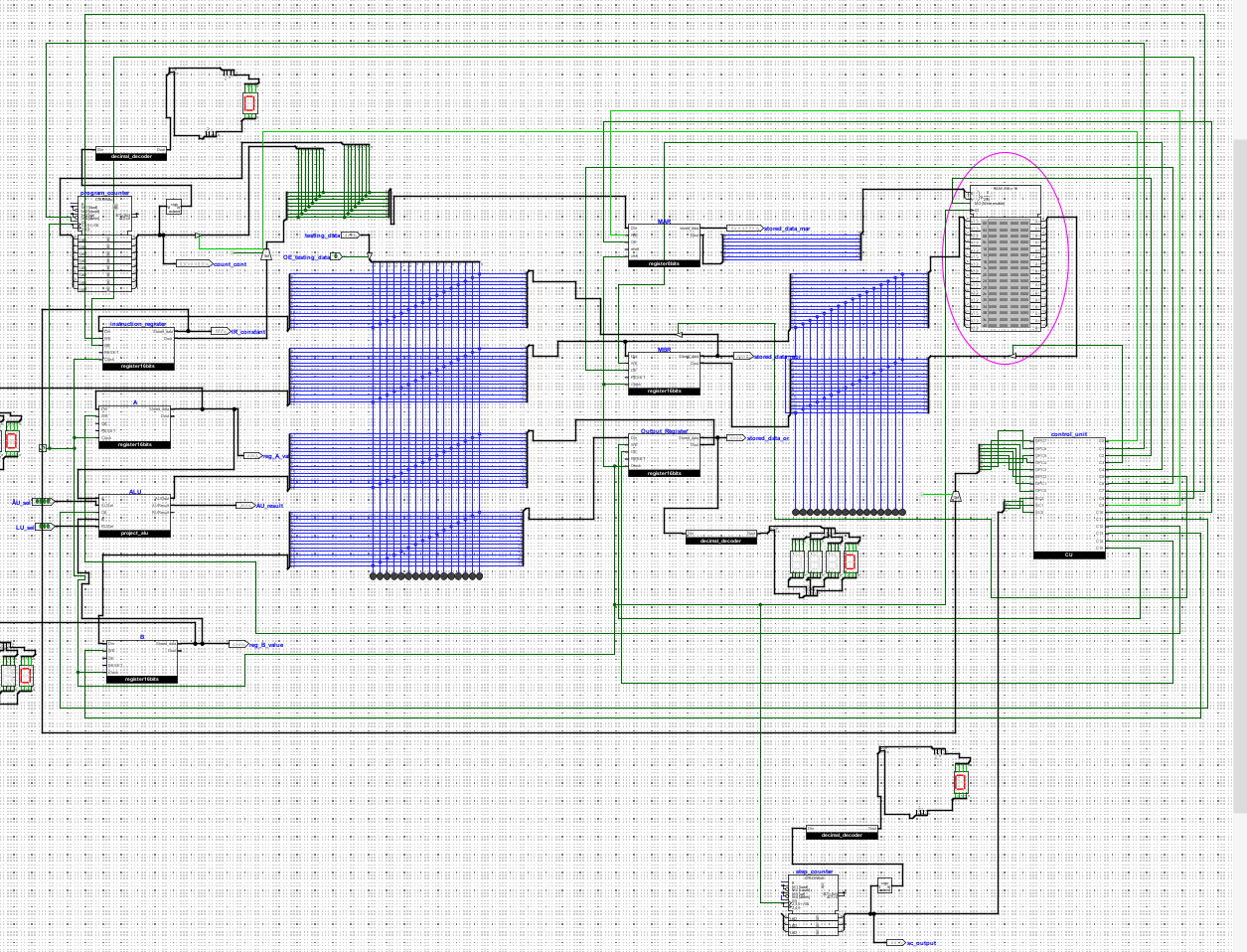

Designing a 16-bit CPU using Logisim Evolution was an engaging journey into the fundamentals of computer architecture. In this project, I designed each component, starting with the Arithmetic Logic Unit (ALU) and progressing to the design of registers and the CPU datapath. Using Logisim's built-in blocks, I implemented various arithmetic and relational operations, ensuring each component interacted seamlessly to process data and instructions. The process wasn't without its challenges, especially debugging complicated wiring jobs and ensuring the correct data flow between components. However, with careful attention to detail and frequent saves to prevent loss of progress, I successfully navigated through each stage of the project. This experience deepened my understanding of Instruction Set Architecture (ISA), control unit design, and how logic gates underpin computing.

Transitioning to the design of a 32-bit CPU using VHDL was a leap into a more robust and powerful realm of hardware description language. Armed with insights from the Logisim project, I tackled the construction of a CPU with enhanced capabilities and complexity. Using VHDL, I went more into the circuit design, crafting a processor that could execute instructions precisely and efficiently. VHDL empowered me to implement a micro-architected control unit, allowing for flexibility and future expansion of the instruction set. Despite transitioning from a graphical interface to a text-based language, the principles remained the same – attention to detail, rigorous testing, and a thorough understanding of the underlying hardware. This project honed my technical skills and instilled in me a profound appreciation for the artistry and craftsmanship inherent in CPU design.